Integrated Thermal Solutions Research Team

Frequency dividers are widely used in high-frequency digital (for example System-On-a-Chip) and analog radio frequency circuits. In telecommunications frequency dividers are most often used to synthesize the carrier signal accurately and fast. The carrier signals are turned out by so called frequency-synthesizers (for example PLL – Phase Locked Loop) which crucially includes frequency dividers. Low consumption, the ability to change the division ratio fast during the operation (even some thousand times per second, for example BlueTooth 1600 times per second) and robust operation is prominently important.

As the integrity and the frequency of the digital integrated circuits have raised, new demands and expectations appeared. Since the area of the chips have continuously grown, the importance of the ability to use clock signals with different frequency at different locations on the chip have raised. Because of this, the clock signal synthesizer centers have to be able to produce signals with dynamically changeable frequency.

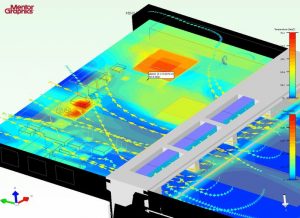

The biggest challenge is to reduce the consumption of the circuits, because as the running frequencies of the integrated circuits raise, their dissipation raises as well, which leads to higher temperatures of the circuits during the running. When the temperature of the circuit increases, the operating points and threshold voltages of the transistors change, which leads to the changing of the delays in the digital circuits and it can cause failures in the operation.

For these new challenges, using Injection Locked Oscillator (ILO) circuits can be a solution. The ILO circuits appeared in the past decade and still an active field of researches.

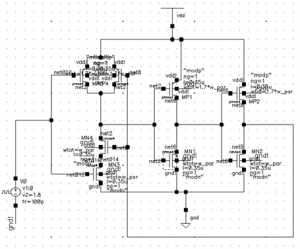

In our work I present the architecture and the functioning of different frequency divider circuits especially focusing on the ILOs. The goal of this work is to design an ILO that will be able to lock on the incoming highfrequency signal and can divide its frequency with the given division ratio. Furthermore, we design an ILO that can be connected to digital circuits to create a frequency divider with adjustable division ratio. During our research we will make on effort on reducing the effect of the deviation of the transistor parameters and the changing of the temperature to consider the design for manufacturability. Taking into account of the previous points we minimize the power consumption of the ILO to create a widely useable circuit.

During our research we use the Cadence 6 integrated circuit design framework with the Austria Micro Systems 350 nm and 180 nm technologies.

Tab Content goes here

Our team

Venerable team leader

Measurement and modelling

Numerical simulation and modelling

Modelling and simulation

- Dávid Szele

BSc student

- Máté Bencze

MSc student